Los ingenieros de Stanford presentan un nuevo chip que aumenta la eficiencia informática de la IA

Los ingenieros de Stanford crearon un chip de IA más eficiente y flexible, que podría llevar el poder de la IA a pequeños dispositivos de borde.

La computación perimetral impulsada por IA ya es omnipresente en nuestras vidas. Los dispositivos como drones, dispositivos portátiles inteligentes y sensores industriales de IoT están equipados con chips habilitados para IA para que la computación pueda ocurrir en el «borde» de Internet, donde se originan los datos. Esto permite el procesamiento en tiempo real y garantiza la privacidad de los datos.

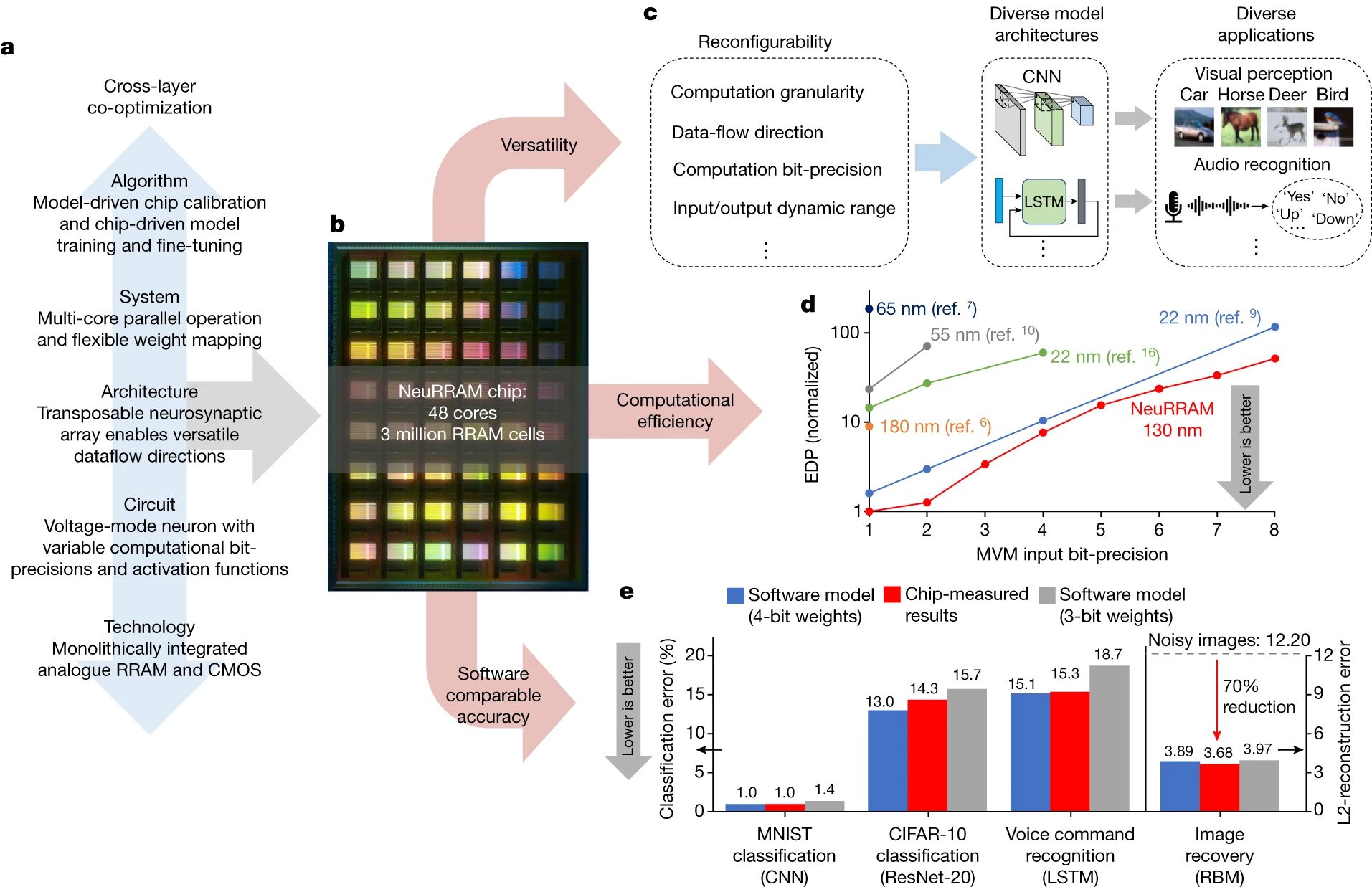

Al combinar computación y memoria en un solo lugar, el chip NeuRRAM podría mejorar la eficiencia y las aplicaciones de una amplia variedad de dispositivos habilitados para IA, como dispositivos portátiles inteligentes, sensores industriales y drones. (Crédito de la imagen: Nicolle Fuller/Sayo Studio)

Sin embargo, las funcionalidades de IA en estos pequeños dispositivos de borde están limitadas por la energía proporcionada por una batería. Por lo tanto, mejorar la eficiencia energética es crucial. En los chips de IA actuales, el procesamiento y el almacenamiento de datos se realizan en lugares separados: una unidad de cómputo y una unidad de memoria. El movimiento frecuente de datos entre estas unidades consume la mayor parte de la energía durante el procesamiento de IA, por lo que reducir el movimiento de datos es la clave para abordar el problema de la energía.

H S felipe wong

Los ingenieros de la Universidad de Stanford han ideado una posible solución: un nuevo chip de memoria resistiva de acceso aleatorio (RRAM) que realiza el procesamiento de IA dentro de la propia memoria, eliminando así la separación entre las unidades de cómputo y memoria. Su chip de «cómputo en memoria» (CIM), llamado NeuRRAM, tiene aproximadamente el tamaño de la yema de un dedo y funciona más con una energía de batería limitada que lo que pueden hacer los chips actuales.

“Hacer esos cálculos en el chip en lugar de enviar información hacia y desde la nube podría permitir una IA más rápida, más segura, más barata y más escalable en el futuro, y brindar a más personas acceso al poder de la IA”, dijo H.-S. Philip Wong , Profesor Willard R. e Inez Kerr Bell en la Escuela de Ingeniería .

Weier Wan

“El problema del movimiento de datos es similar a pasar ocho horas de viaje durante una jornada laboral de dos horas”, agregó Weier Wan, un recién graduado de Stanford que dirige este proyecto. “Con nuestro chip, estamos mostrando una tecnología para enfrentar este desafío”.

Presentaron NeuRRAM en un artículo reciente en la revista Nature . Si bien la computación en memoria ha existido durante décadas, este chip es el primero en demostrar una amplia gama de aplicaciones de IA en hardware, en lugar de solo a través de la simulación.

a , Las cooptimizaciones de capas cruzadas en toda la pila del diseño permiten a NeuRRAM ofrecer simultáneamente una alta versatilidad, eficiencia computacional y precisión de inferencia comparable al software. b , Micrografía del chip NeuRRAM. c , la reconfigurabilidad en varios aspectos del diseño permite a NeuRRAM implementar diversos modelos de IA para una amplia variedad de aplicaciones. d , Comparación de EDP, una métrica de rendimiento y eficiencia energética comúnmente utilizada entre el hardware CIM basado en RRAM reciente. e , la precisión de la inferencia totalmente medida por hardware en NeuRRAM es comparable a los modelos de software cuantificados en pesos de 4 bits en varios puntos de referencia de IA.

Poniendo poder de cómputo en el dispositivo

Para superar el cuello de botella del movimiento de datos, los investigadores implementaron lo que se conoce como computación en memoria (CIM), una nueva arquitectura de chip que realiza la computación de IA directamente dentro de la memoria en lugar de unidades de computación separadas. La tecnología de memoria que utilizó NeuRRAM es la memoria resistiva de acceso aleatorio (RRAM). Es un tipo de memoria no volátil (memoria que retiene datos incluso cuando se apaga) que ha surgido en productos comerciales. RRAM puede almacenar grandes modelos de IA en un área pequeña y consumir muy poca energía, lo que los hace perfectos para dispositivos periféricos de tamaño pequeño y bajo consumo.

Si bien el concepto de chips CIM está bien establecido y la idea de implementar la computación de IA en RRAM no es nueva, “esta es una de las primeras instancias en integrar una gran cantidad de memoria directamente en el chip de red neuronal y presentar todos los resultados de referencia. a través de mediciones de hardware”, dijo Wong, coautor principal del artículo de Nature .

La arquitectura de NeuRRAM permite que el chip realice cálculos analógicos en memoria a baja potencia y en un área compacta. Fue diseñado en colaboración con el laboratorio de Gert Cauwenberghs en la Universidad de California, San Diego, quien fue pionero en el diseño de hardware neuromórfico de baja potencia. La arquitectura también permite la reconfiguración en las direcciones del flujo de datos, admite varias estrategias de mapeo de cargas de trabajo de IA y puede funcionar con diferentes tipos de algoritmos de IA, todo sin sacrificar la precisión del cálculo de IA.

Para mostrar la precisión de las habilidades de IA de NeuRRAM, el equipo probó cómo funcionaba en diferentes tareas. Descubrieron que tiene una precisión del 99 % en el reconocimiento de letras del conjunto de datos MNIST, una precisión del 85,7 % en la clasificación de imágenes del conjunto de datos CIFAR-10, una precisión del 84,7 % en el reconocimiento de comandos de voz de Google y una reducción del 70 % en el error de reconstrucción de imágenes en un Bayesiano tarea de recuperación de imagen.

“La eficiencia, la versatilidad y la precisión son aspectos importantes para una adopción más amplia de la tecnología”, dijo Wan. “Pero realizarlos todos a la vez no es simple. Co-optimizar la pila completa desde el hardware hasta el software es la clave”.

“Este codiseño de pila completa es posible gracias a un equipo internacional de investigadores con experiencia diversa”, agregó Wong.

Alimentando los cálculos de borde del futuro

En este momento, NeuRRAM es una prueba de concepto física, pero necesita más desarrollo antes de que esté listo para traducirse en dispositivos de borde reales.

Pero esta combinación de eficiencia, precisión y capacidad para realizar diferentes tareas muestra el potencial del chip. “Tal vez hoy se usa para realizar tareas simples de IA, como la detección de palabras clave o la detección humana, pero mañana podría permitir una experiencia de usuario completamente diferente. Imagine el análisis de video en tiempo real combinado con el reconocimiento de voz, todo dentro de un dispositivo pequeño”, dijo Wan. “Para darnos cuenta de esto, debemos continuar mejorando el diseño y escalando la RRAM a nodos de tecnología más avanzada”.

priyanka raina

“Este trabajo abre varias vías de investigación futura sobre ingeniería de dispositivos RRAM y modelos de programación y diseño de redes neuronales para computación en memoria, para hacer que esta tecnología sea escalable y utilizable por los desarrolladores de software”, dijo Priyanka Raina , profesora asistente de ingeniería eléctrica. y coautor del artículo.

Si tienen éxito, los chips de cómputo en memoria RRAM como NeuRRAM tienen un potencial casi ilimitado. Podrían integrarse en campos de cultivo para realizar cálculos de IA en tiempo real para ajustar los sistemas de riego a las condiciones actuales del suelo. O podrían convertir las gafas de realidad aumentada de unos cascos toscos con una funcionalidad limitada en algo más parecido a la pantalla de visualización de Tony Stark en las películas de Iron Man y Avengers (sin amenazas intergalácticas o del multiverso, es de esperar).

Si se produjeran en masa, estos chips serían lo suficientemente baratos, lo suficientemente adaptables y de baja potencia como para que pudieran usarse para avanzar en tecnologías que ya mejoran nuestras vidas, dijo Wong, como en dispositivos médicos que permiten el monitoreo de la salud en el hogar.

También se pueden usar para resolver desafíos sociales globales: los sensores habilitados para IA desempeñarían un papel en el seguimiento y el abordaje del cambio climático. “Al tener este tipo de dispositivos electrónicos inteligentes que se pueden colocar en casi cualquier lugar, puede monitorear el mundo cambiante y ser parte de la solución”, dijo Wong. “Estos chips podrían usarse para resolver todo tipo de problemas, desde el cambio climático hasta la seguridad alimentaria”.

Otros coautores de este trabajo incluyen investigadores de la Universidad de California en San Diego (codirector), la Universidad de Tsinghua, la Universidad de Notre Dame y la Universidad de Pittsburgh. El exestudiante graduado de Stanford Sukru Burc Eryilmaz también es coautor. Wong es miembro de Stanford Bio-X y del Instituto de Neurociencias Wu Tsai , y afiliado al Instituto Precourt para la Energía . También es director de la facultad de Stanford Nanofabrication Facility y codirector de la facultad fundadora de Stanford SystemX Alliance , un programa afiliado industrial en Stanford centrado en sistemas de construcción.

Esta investigación fue financiada por National Science Foundation Expeditions in Computing, SRC JUMP ASCENT Center, Stanford SystemX Alliance , Stanford NMTRI , Beijing Innovation Center for Future Chips, National Natural Science Foundation of China y Office of Naval Research

Hacer visitas medicas a domicilio guiadas por Inteligencia artificial